Inheritance diagram for dwmac:

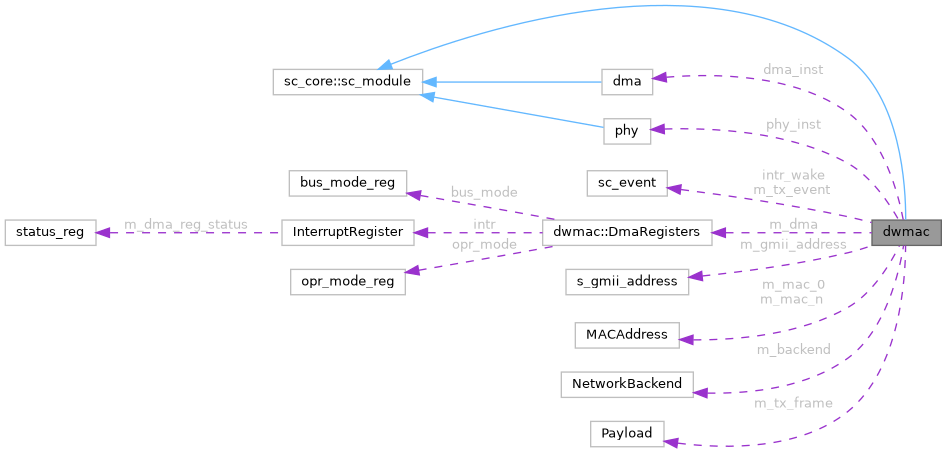

Collaboration diagram for dwmac:

Classes | |

| class | DmaRegisters |

Public Member Functions | |

| void | set_backend (NetworkBackend *backend) |

| dwmac (sc_core::sc_module_name name) | |

| uint32_t | read_word (uint32_t address) |

| void | write_word (uint32_t address, uint32_t data) |

| void | b_transport (tlm::tlm_generic_payload &trans, sc_core::sc_time &delay) |

| virtual void | payload_recv (Payload &frame) |

Static Public Member Functions | |

| static void | eth_rx_sc (void *opaque, Payload &frame) |

| static int | eth_can_rx_sc (void *opaque) |

Public Attributes | |

| sc_core::sc_out< bool > | intr0 |

| sc_core::sc_out< bool > | intr1 |

| tlm_utils::simple_target_socket< dwmac, DEFAULT_TLM_BUSWIDTH > | socket |

| dma | dma_inst |

| phy | phy_inst |

| NetworkBackend * | m_backend |

| Payload | m_tx_frame |

Protected Member Functions | |

| void | reset () |

| void | interrupts_fire (uint32_t interrupts) |

| void | interrupts_clear (uint32_t interrupts) |

| bool | read_tx_desc (dma_desc *desc) |

| bool | read_rx_desc (dma_desc *desc) |

| bool | tx () |

| bool | rx (Payload &frame) |

| void | move_to_next_tx_desc (dma_desc &desc) |

| void | tx_thread () |

| void | intr_thread () |

Protected Attributes | |

| bool | warn_anregs = true |

| sc_core::sc_event | m_tx_event |

| sc_core::sc_event | intr_wake |

| DmaRegisters | m_dma |

| uint32_t | m_configuration |

| uint32_t | m_frame_filter |

| uint32_t | m_hash_table_hi |

| uint32_t | m_hash_table_lo |

| union s_gmii_address | m_gmii_address |

| uint32_t | m_gmii_data |

| uint32_t | m_flow_control |

| uint32_t | m_vlan_tag |

| uint32_t | m_pmt |

| MACAddress | m_mac_0 |

| MACAddress | m_mac_n [MACn_COUNT] |

| uint32_t | m_htbl [8] |

| uint32_t | m_int_mask |

| uint32_t | m_axi_bus_mode |

Static Protected Attributes | |

| static const uint32_t | DMA_BUS_MODE = 0x1000 |

| static const uint32_t | DMA_TX_POLL = 0x1004 |

| static const uint32_t | DMA_RX_POLL = 0x1008 |

| static const uint32_t | DMA_RX_DESC_LIST_ADDR = 0x100C |

| static const uint32_t | DMA_TX_DESC_LIST_ADDR = 0x1010 |

| static const uint32_t | DMA_STATUS = 0x1014 |

| static const uint32_t | DMA_OPERATION_MODE = 0x1018 |

| static const uint32_t | DMA_INTERRUPTS = 0x101C |

| static const uint32_t | DMA_COUNTERS = 0x1020 |

| static const uint32_t | DMA_RX_INT_WDT = 0x1024 |

| static const uint32_t | DMA_AXI_BUS_MODE = 0x1028 |

| static const uint32_t | DMA_CURRENT_TX_DESC = 0x1048 |

| static const uint32_t | DMA_CURRENT_RX_DESC = 0x104C |

| static const uint32_t | DMA_CURRENT_TX_BUF = 0x1050 |

| static const uint32_t | DMA_CURRENT_RX_BUF = 0x1054 |

| static const uint32_t | HW_FEATURE = 0x1058 |

| static const uint32_t | DWMAC_VERSION_VALUE = 0x0010 |

| static const uint32_t | DWMAC_CONFIGURATION = 0x0000 |

| static const uint32_t | DWMAC_FRAME_FILTER = 0x0004 |

| static const uint32_t | DWMAC_HASH_TABLE_HI = 0x0008 |

| static const uint32_t | DWMAC_HASH_TABLE_LO = 0x000C |

| static const uint32_t | DWMAC_GMII_ADDRESS = 0x0010 |

| static const uint32_t | DWMAC_GMII_DATA = 0x0014 |

| static const uint32_t | DWMAC_FLOW_CONTROL = 0x0018 |

| static const uint32_t | DWMAC_VLAN_TAG = 0x001C |

| static const uint32_t | DWMAC_VERSION = 0x0020 |

| static const uint32_t | DWMAC_WAKE_UP_FILTER = 0x0028 |

| static const uint32_t | DWMAC_PMT = 0x002C |

| static const uint32_t | DWMAC_INTERRUPT = 0x0038 |

| static const uint32_t | DWMAC_INTERRUPT_MASK = 0x003C |

| static const uint32_t | DWMAC_AN_CONTROL = 0x00C0 |

| static const uint32_t | DWMAC_AN_STATUS = 0x00C4 |

| static const uint32_t | DWMAC_AN_ADVERTISEMENT = 0x00C8 |

| static const uint32_t | DWMAC_AN_LINK_PARTNER_ABILITY = 0x00CC |

| static const uint32_t | DWMAC_AN_EXPANSION = 0x00D0 |

| static const uint32_t | DWMAC_MAC0_HI = 0x0040 |

| static const uint32_t | DWMAC_MAC0_LO = 0x0044 |

| static const uint32_t | DWMAC_MACn = 0x0048 |

| static const uint32_t | DWMAC_MMC_CONTROL = 0x0100 |

| static const uint32_t | DWMAC_MMC_RX_INT = 0x0104 |

| static const uint32_t | DWMAC_MMC_TX_INT = 0x0108 |

| static const uint32_t | DWMAC_MMC_RX_INT_MASK = 0x010C |

| static const uint32_t | DWMAC_MMC_TX_INT_MASK = 0x0110 |

| static const uint32_t | DWMAC_MMC_IPC_RX_INT_MASK = 0x0200 |

| static const uint32_t | DWMAC_MMC_IPC_RX_INT = 0x0208 |

| static const uint32_t | MACn_COUNT = 15 |

The documentation for this class was generated from the following files:

- systemc-components/macs/dwmac/include/dwmac.h

- systemc-components/macs/dwmac/src/dwmac.cc